- 您现在的位置:买卖IC网 > Sheet目录3876 > PIC16F1526-I/PT (Microchip Technology)MCU 14KB FLASH 768B RAM 64-TQFP

191

7810C–AVR–10/12

Atmel ATmega328P [Preliminary]

Bit 0 – UCPOLn: Clock Polarity

This bit is used for synchronous mode only. Write this bit to zero when asynchronous mode is

used. The UCPOLn bit sets the relationship between data output change and data input sample,

and the synchronous clock (XCKn).

19.10.5

UBRRnL and UBRRnH – USART Baud Rate Registers

Bit 15:12 – Reserved Bits

These bits are reserved for future use. For compatibility with future devices, these bit must be

written to zero when UBRRnH is written.

Bit 11:0 – UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART baud rate. The UBRRnH contains the four

most significant bits, and the UBRRnL contains the eight least significant bits of the USART

baud rate. Ongoing transmissions by the Transmitter and Receiver will be corrupted if the baud

rate is changed. Writing UBRRnL will trigger an immediate update of the baud rate prescaler.

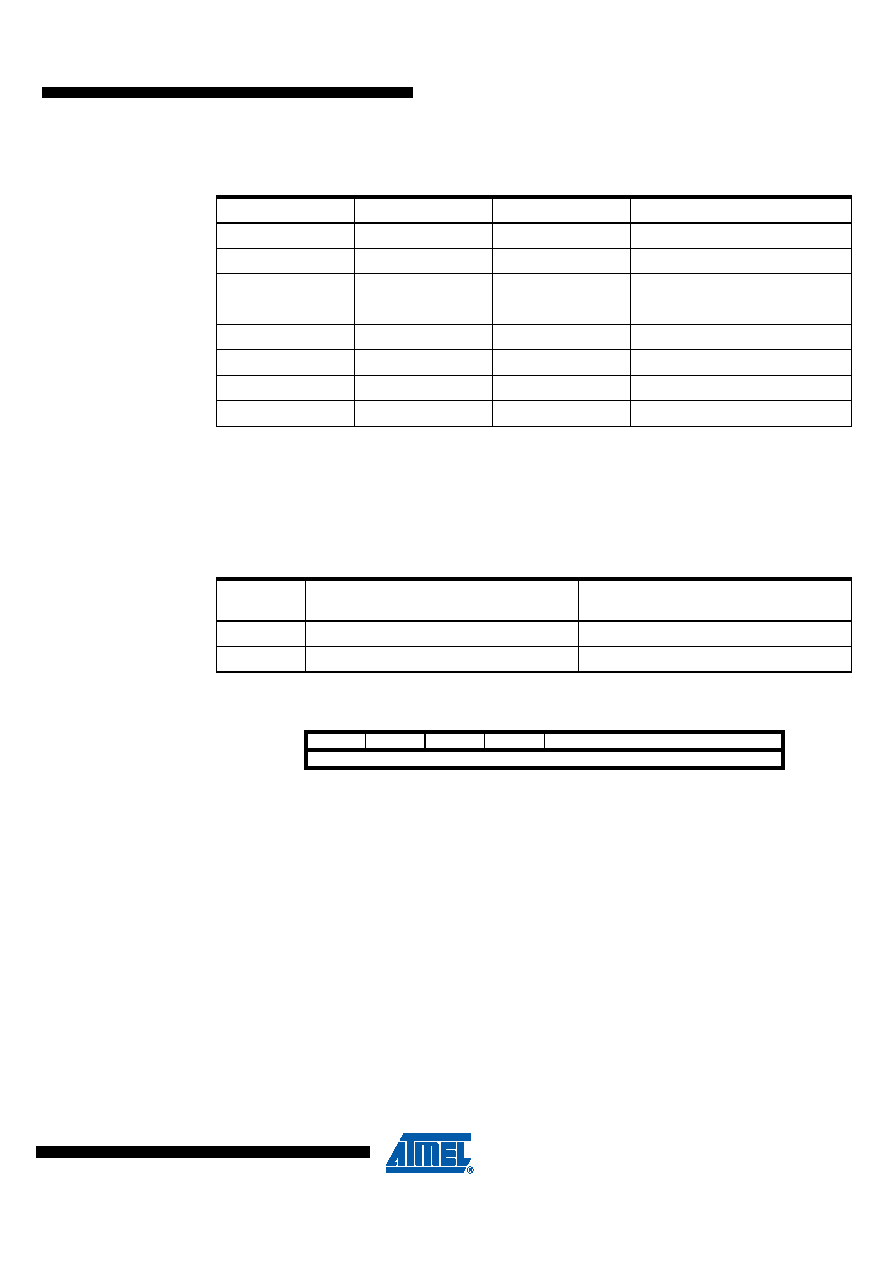

Table 19-7.

UCSZn Bits Settings

UCSZn2

UCSZn1

UCSZn0

Character Size

00

0

5-bit

00

1

6-bit

01

0

7-bit

01

1

8-bit

1

0

Reserved

1

0

1

Reserved

1

0

Reserved

11

1

9-bit

Table 19-8.

UCPOLn Bit Settings

UCPOLn

Transmitted Data Changed (Output of

TxDn Pin)

Received Data Sampled (Input on RxDn

Pin)

0

Rising XCKn Edge

Falling XCKn Edge

1

Falling XCKn Edge

Rising XCKn Edge

Bit

151413

1211

10

9

8

–

UBRRn[11:8]

UBRRnH

UBRRn[7:0]

UBRRnL

76

54

32

10

Read/Write

R

R/W

Initial Value

0

00

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL401-I/SO

IC MCU 16BIT 8KB FLASH 20-SOIC

PIC18F13K50-I/MQ

IC PIC MCU FLASH 512KX8 20-QFN

PIC16F1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC24F16KL402-I/SS

IC MCU 16BIT 16KB FLASH 28-SSOP

PIC16LF1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC16C58B-20/P

IC MCU OTP 2KX12 18DIP

PIC18F24K20-I/SP

IC PIC MCU FLASH 8KX16 28-DIP

PIC16F1936-I/SP

IC PIC MCU FLASH 512KX14 28SPDIP

相关代理商/技术参数

PIC16F1526-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-TQFP 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20MHz, TQFP-64

PIC16F1526T-I/MR

功能描述:8位微控制器 -MCU 14KB FL 768B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1526T-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-QFN 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20 MHz, 64-QFN; Controller Family/Series:PIC16F; Core Size:8bit; No. of I/O's:54; Program Memory Size:28KB; RAM Memory Size:1536Byte; CPU Speed:20MHz; Oscillator Type:External, Internal; No. of Timers:9 ;RoHS Compliant: No

PIC16F1527-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT